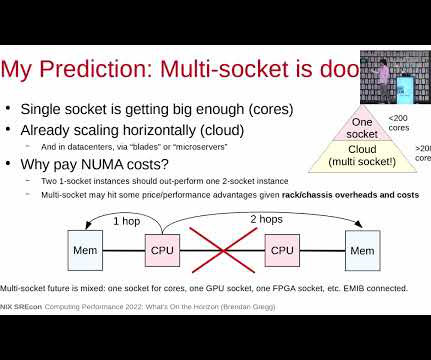

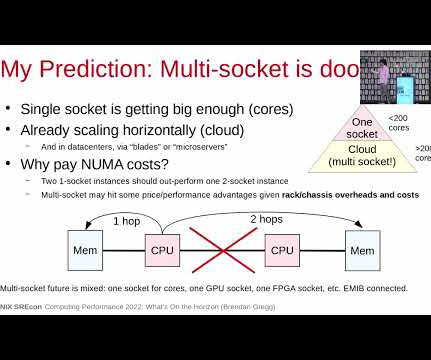

USENIX SREcon APAC 2022: Computing Performance: What's on the Horizon

Brendan Gregg

FEBRUARY 28, 2023

I'm now program co-chair for SREcon 2023 APAC, and our 2023 conference is June 14-16 in Singapore. And now, helping bring USENIX conferences to Australia by giving the first keynote: I could not have scripted or expected it. The call for participation ends on March 2nd 23:59 SGT!

Let's personalize your content