Understanding operational 5G: a first measurement study on its coverage, performance and energy consumption

The Morning Paper

OCTOBER 4, 2020

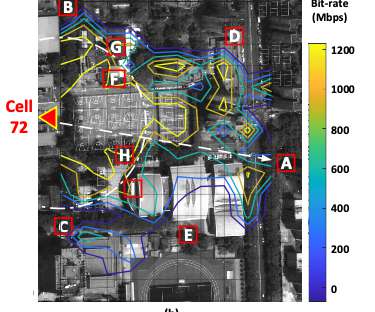

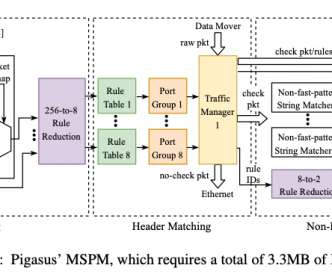

Understanding operational 5G: a first measurement study on its coverage, performance and energy consumption , Xu et al., What is the end-to-end throughput and latency, and where are the bottlenecks? energy consumption). Future 5G Standalone Architecture (SA) deployments with a native 5G control plane will not have this problem.

Let's personalize your content