USENIX SREcon APAC 2022: Computing Performance: What's on the Horizon

Brendan Gregg

FEBRUARY 28, 2023

I didn't end up getting published in SysAdmin directly, but my performance work did make it as a feature article (thanks Matty).

Brendan Gregg

FEBRUARY 28, 2023

I didn't end up getting published in SysAdmin directly, but my performance work did make it as a feature article (thanks Matty).

Brendan Gregg

FEBRUARY 28, 2023

As for attending USENIX conferences: I finally started attending and speaking at them in 2010 when a community manager encouraged me to (thanks Deirdre Straughan), and since then I've met many friends and connections, including Amy who is now USENIX President, and Rikki with whom I co-chaired the USENIX LISA18 conference.

This site is protected by reCAPTCHA and the Google Privacy Policy and Terms of Service apply.

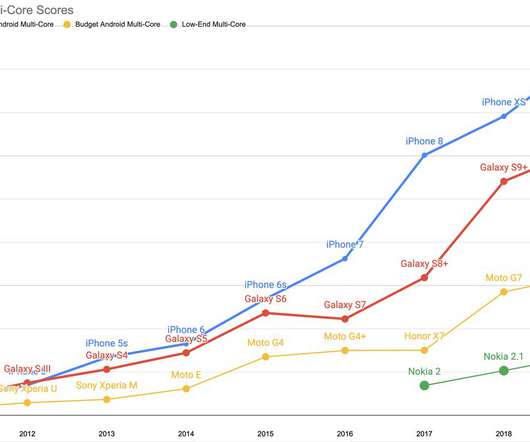

Alex Russell

MARCH 6, 2021

A then-representative $200USD device had 4-8 slow (in-order, low-cache) cores, ~2GiB of RAM, and relatively slow MLC NAND flash storage. Advances in browser content processing. Hardware Past As Performance Prologue. The Moto G4 , for example. Modern network performance and availability. Content Is Dead, Long Live Content.

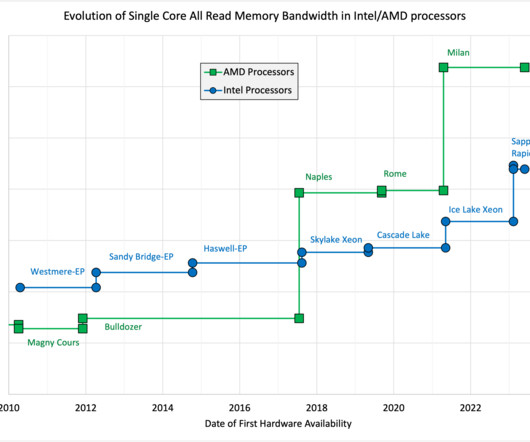

John McCalpin

APRIL 25, 2023

For most high-end processors these values have remained in the range of 75% to 85% of the peak DRAM bandwidth of the system over the past 15-20 years — an amazing accomplishment given the increase in core count (with its associated cache coherence issues), number of DRAM channels, and ever-increasing pipelining of the DRAMs themselves.

Let's personalize your content